nepangkeun:

Dina lingkungan téknologi canggih ayeuna, paménta pikeun papan sirkuit berkinerja tinggi terus ningkat.Nalika jumlah lapisan dina papan sirkuit nambahan, janten pajeulitna pikeun mastikeun alignment anu leres antara lapisan. Masalah anu teu cocog lapisan, sapertos bédana panjang ngalacak antara lapisan, tiasa parah mangaruhan pungsionalitas sareng réliabilitas alat éléktronik.

Ngartos mismatch antara lapisan:

Lapisan mismatch nujul kana bédana dina renik panjangna atawa ukuran antara lapisan dina papan sirkuit multilayer. Kasaluyuan ieu tiasa nyababkeun masalah integritas sinyal, gangguan éléktromagnétik, sareng degradasi kinerja sacara umum. Ngarengsekeun masalah ieu merlukeun kaahlian dina desain, perenah jeung prosés manufaktur.

Metoda Capel pikeun ngajawab mismatch antara lapisan:

1. Alat sareng téknologi desain canggih:

Capel gaduh tim R&D mandiri anu saé sareng kuat anu salawasna aya di payuneun kamajuan téknologi papan sirkuit. Kaahlian aranjeunna dina ngagunakeun alat sareng téknik desain anu canggih ngabantosan ngaidentipikasi masalah anu teu cocog lapisan-ka-lapisan dina awal fase desain.

2. Taliti milih bahan:

Pilihan bahan maénkeun peran kritis dina ngaminimalkeun masalah mismatch antar-lapisan. pangalaman proyék éksténsif Capel urang ngamungkinkeun aranjeunna taliti milih bahan kalawan sipat luyu, kayaning koefisien low tina ékspansi termal (CTE) jeung konstanta diéléktrik konsisten, pikeun mastikeun parobahan dimensi minimal.

3. Prosés manufaktur precision:

Fasilitas canggih sareng prosés manufaktur Capel direkayasa pikeun ngahontal precision tinggi sareng akurasi alignment. Ukuran kontrol kualitas anu ketat mastikeun yén teu cocog lapisan-ka-lapisan diréduksi jadi minimum, ngajamin kinerja dewan punjul.

4. Desain impedansi dikawasa:

Insinyur Capel parantos ngasah kaahlianna dina ngadalikeun desain impedansi, aspék konci pikeun ngirangan mismatch antara lapisan. Ku persis ngadalikeun stackup diéléktrik jeung ngambah lebar, aranjeunna ngaoptimalkeun integritas sinyal jeung ngaleutikan mismatches jalur transmisi antara lapisan.

5. Tes lengkep sareng verifikasi:

Capel daun euweuh batu unturned lamun datang ka nguji sarta validasi. Sateuacan produk ahir dikirimkeun, uji listrik sareng mékanis anu komprehensif diperyogikeun pikeun mastikeun papan nyumponan standar kualitas pangluhurna. Pendekatan anu cermat ieu ngabantosan ngaidentipikasi sareng ngabenerkeun masalah anu teu cocog lapisan-ka-lapisan.

Naha milih Capel:

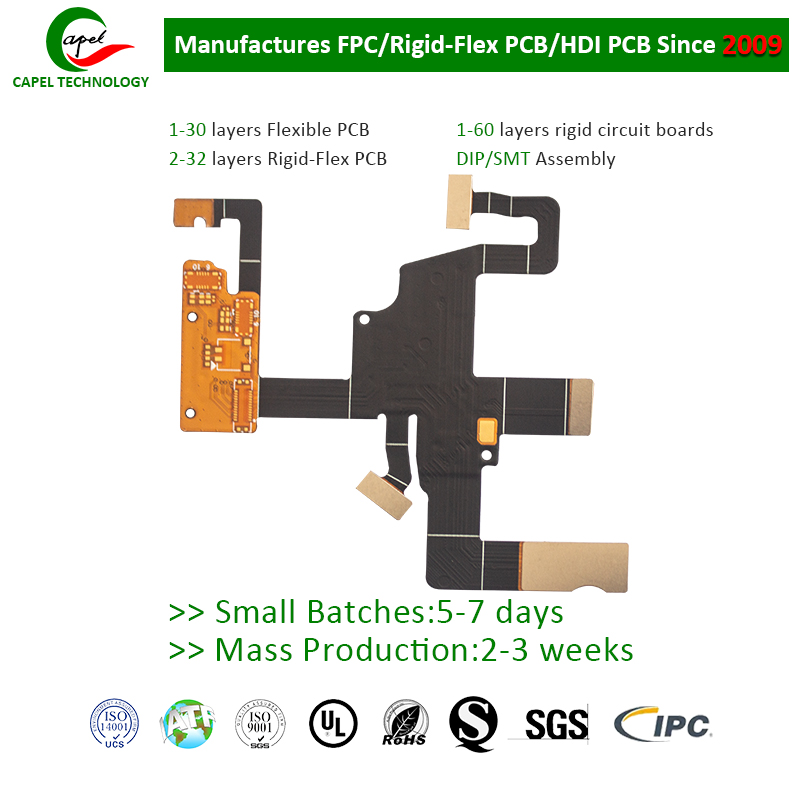

Cakap capel ngeunaan kaunggulan dina produksi papan sirkuit, ditambah ku pangalaman proyék anu éksténsif, ngajantenkeun aranjeunna pasangan anu idéal pikeun ngarengsekeun masalah interlayer anu teu cocog dina papan sirkuit 16-lapisan. Komitmen maranéhna pikeun panalungtikan sarta pamekaran ensures yén maranéhna tetep dihareupeun tren industri, nyadiakeun konsumén jeung solusi motong-ujung anu éféktif alamat tantangan mismatch antar-lapisan.

Kasimpulanana:

Lapisan masalah mismatch dina 16-lapisan circuit boards, kayaning béda dina panjang renik antara lapisan, bisa jadi halangan daunting. Nanging, kalayan kaahlian sareng kamampuan Capel, tantangan ieu tiasa suksés diatasi. Ngaliwatan parabot design canggih, Pilihan bahan ati, prosés manufaktur precision, desain impedansi dikawasa jeung nguji teleb, Capel nyadiakeun solusi ngaropéa nu mastikeun optimal lapisan-to-lapisan alignment jeung kinerja dewan unggul. Percanten 15 taun pangalaman Capel sareng tim R&D anu ngarah di industri pikeun ngajalankeun proyék anjeun pikeun suksés sareng ngarebut unggal kasempetan dina rohangan téknologi anu terus-terusan ieu.

waktos pos: Sep-30-2023

Balik deui